Lapran Akhir Modul 1 (Percobaan 1)

2. ALAT dan BAHAN [Kembali]

- Logika NOT

- Logika AND

- Logika OR

- Logika XOR

- Logika NAND

- Logika NOR

- Logika XNOR

- Logicstate

- Logicprobe

- Clock

- Osiloscope

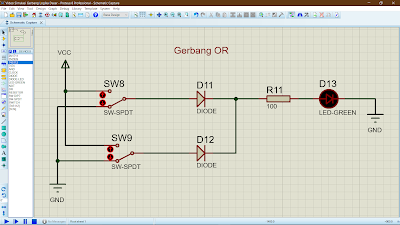

Gambar 3.2

4. PRINSIP KERJA RANGKAIAN [Kembali]

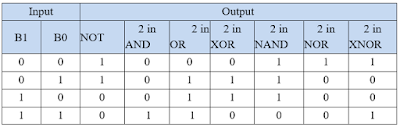

Pada rangkaian yang disimulasikan menggunakan Gerbang Logika NOT, AND, OR, XOR, NAND, NOR, dan XNOR. Pada gambar 3.1 tiap gerbang logika akan di uji dengan logicstate sebagai input dan logicprobe sebagai output. Ketika B0 di beri nilai 0 dan B1 bernilai 0, pada Logika NOT bernilai 1, Logika AND bernilai 0, Logika OR bernilai 0, Logika XOR bernilai 0, Logika NAND bernilai 1, Logika NOR bernilai 1, dan Logika XNOR bernilai 1.

Jika B0 bernilai 0 dan B1 bernilai 1, maka pada Logika NOT bernilai 1, Logika AND bernilai 0, Logika OR bernilai 1, Logika XOR bernilai 1, Logika NAND bernilai 1, Logika NOR bernilai 0, dan Logika XNOR bernilai 0.

Jika B0 bernilai 1 dan B1 bernilai 0, maka pada Logika NOT bernilai 0, Logika AND bernilai 0, Logika OR bernilai 1, Logika XOR bernilai 1, Logika NAND bernilai 1, Logika NOR bernilai 0, dan Logika XNOR bernilai 0.

Dan jika B0 bernilai 1 dan B1 bernilai 1, maka pada Logika NOT bernilai 0, Logika AND bernilai 1, Logika OR bernilai 1, Logika XOR bernilai 0, Logika NAND bernilai 0, Logika NOR bernilai 0, dan Logika XNOR bernilai 1.

Sesuai dengan hasil yang telah didapatkan pada tabel kebenaran berikut.

Pada gambar 3.2 tiap gerbang logika akan di uji dengan menambahkan clock di inputnya dan juga menggunakan osiloscope untuk melihat hasil dari clock yanng di hasilkan oleh gerbang logika yang di uji atau di simulasikan.

Pada gerbang NOT input di pengaruhi oleh clock dan pada osilocope dapat dilihat hasil dari gelombang atau outputnya. Seterusnya hingga ke semua gerbang logika telah di uji dan untuk tiap output pada gerbang-gerbang logika tersebut dapat dilihat pada tabel berikut.

5. VIDEO RANGKAIAN [Kembali]

- Jelaskan prinsip kerja dari rangkaian dalam gerbang AND, OR, NOT, NOR, dan NAND

1. Logika AND

Ketika rangkaian di aliri vcc, dua saklar pada rangkaian dalam Logika AND akan dialiri arus vcc yang melewati R1 dan 2 buah diode dengan melalui kaki katodanya dan menuju R2 denga outputnya LED yang menandakan apakah rangkaian berfunngsi seperti pada gambar.

2. Logika OR

Ketika rangkaian di aliri Vcc, kedua saklar rangkaian akan di aliri arus dan jika salah satu atau kedua saklar di aliri arus melewati diode melalui kaki anoda ke katoda dan menuju R11 dan menunjukkan bahwa output (LED) hidup, seperti pada gambar.

3. Logika NOT

Ketika rangkaian di aliri vcc, dan saklar mati atau bernilai 0, maka arus yang mengalir di rangkaian akan menuju melewati R10 dan kaki transistor, maka output menghasilkan nilai 1 atau LED akan hidup. Begitupun sebaliknya, jika saklar hidup atau bernilai 1 maka arus akan mengalir melalui R9, R10, dan kaki transistor yang menyebabkan LED akan mati atau bernilai 0.

4. Logika NOR

Output NOR akan bernilai 1 jika input pada kedua kakinya bernilai 0, dan Inputnya akan bernilai 0 jika kedua inputnya bernilai 1. Jika salah satu kakinya bernilai 1 dan yang lain bernilai 0, ouputnya tetap bernilai 0.

5. Logika NAND

Output NAND akan bernilai 1 jika inputnya bernilai 0 atau hanya salah satu kaki saja yang bernilai 1. Dan Outputnya akan bernilai 0 jika kedua kaki inputnya bernilai 1.

2. Bandingkan dan analisa hasil percobaan dengan masing-masing tabel kebenaran gerbang logika

Jawab:

Dari hasil yang telah di simulasikan dari rangkaian tersebut, hasil tiap gerbang logika berbeda-beda dikarenakan prinsip kerja dari gerbang logika tersebut yang juga berbeda-beda. Dan setelah di analisa untuk hasil yang telah di uji juga sama dengan tabel kebenaran dari tiap gerbang logika.

7. LINK DOWNLOAD [Kembali]

- Download HTML : KLIK DISINI !!!

- Download Rangkaian (Proteus) : KLIK DISINI !!!

- Download Video : KLIK DISINI !!!

Tidak ada komentar:

Posting Komentar